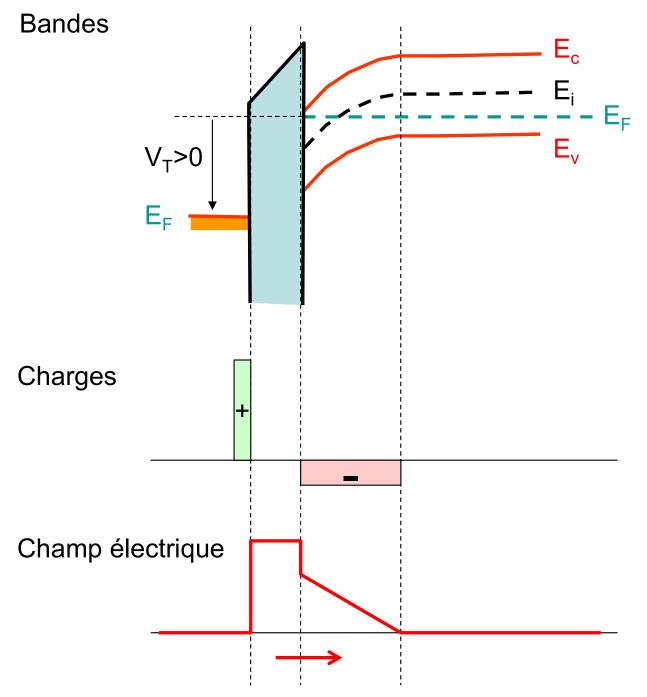

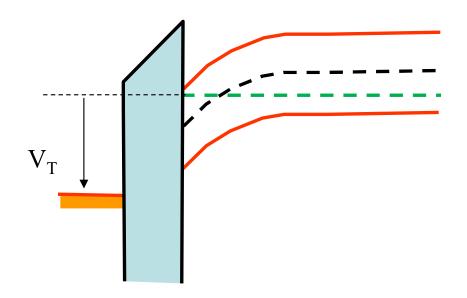

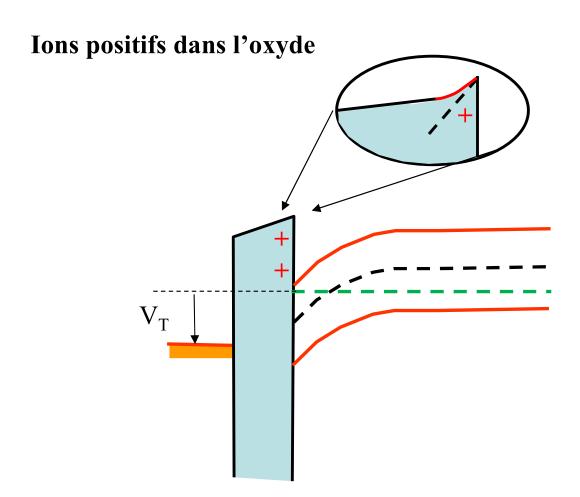

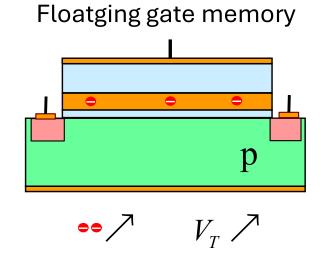

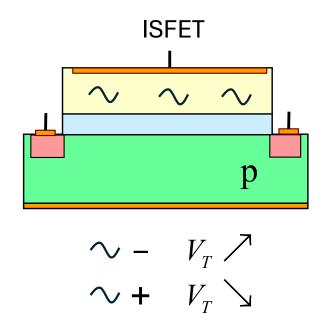

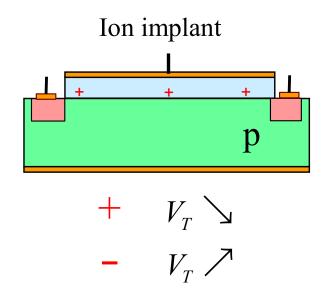

Après introduction de charges fixes positives à l'interface:

|                                                               | Augmente | Diminue     | Reste fixe    |

|---------------------------------------------------------------|----------|-------------|---------------|

| Potentiel de surface $\psi_S$                                 |          |             | <b>&gt;</b>   |

| Charges d'espace dans la zone de déplétion                    |          |             | $\rightarrow$ |

| Champ électrique dans l'oxyde                                 |          |             |               |

| Charges dans le métal                                         |          | <b>&gt;</b> |               |

| Tension électrique sur le métal (Tension de threshold $V_T$ ) |          | <b>&gt;</b> |               |

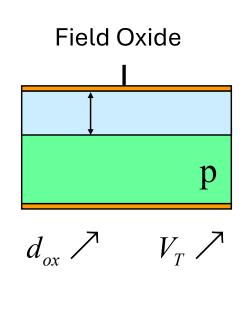

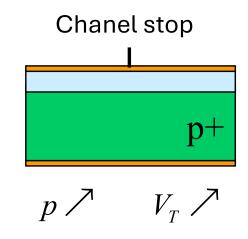

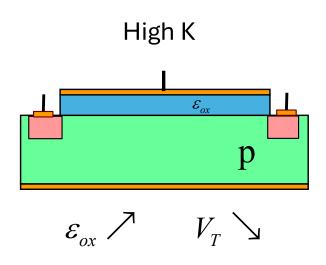

## Situation de depart sans ion dans l'oxyde

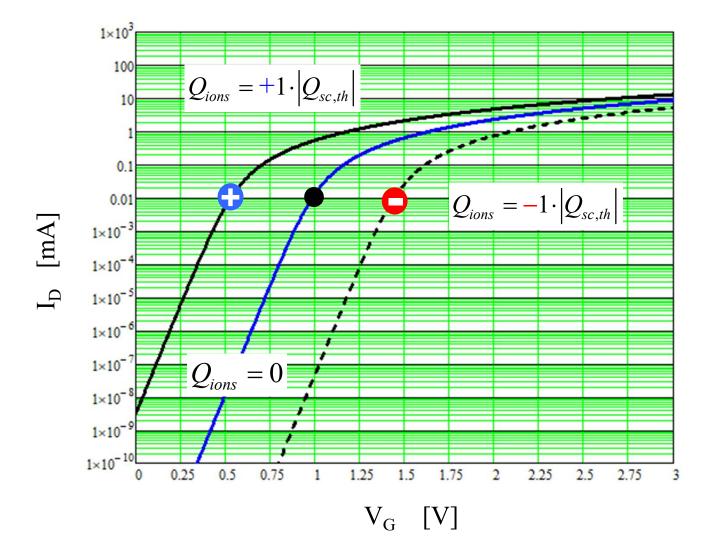

Réduction du threshold

$V_T = V_{T0} - \frac{Q_{ion}}{C_{ox}}$

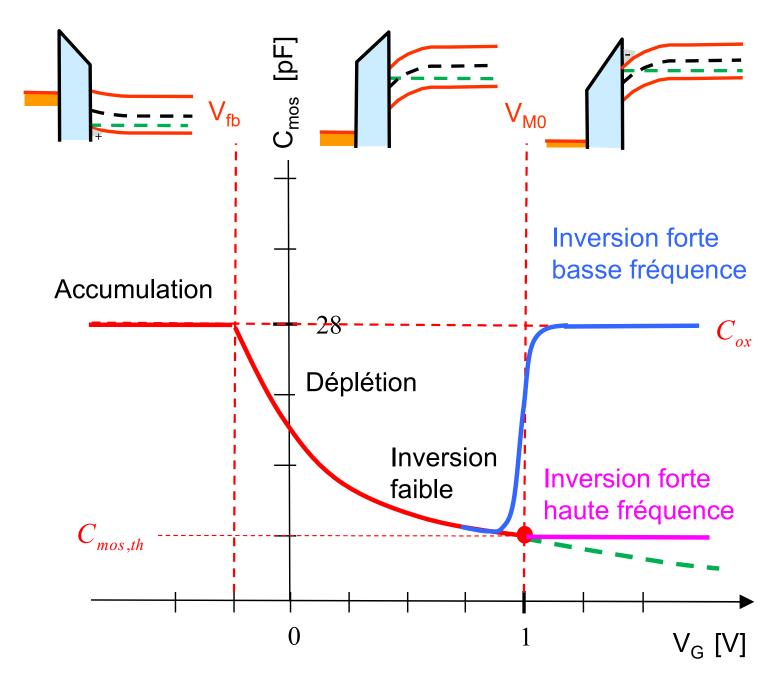

$$N_A=10^{17} \text{ cm}^{-3}$$

$$\varepsilon_{ox}=4$$

$$d_{ox}=10 \text{ nm}$$

$$|Q_{sc,th}|=1.6\cdot10^{-15} \left[C/um^2\right]$$

n = 1.27 dans les trois cas

#### Déplétion profonde

$$C_{mos,th} = \frac{C_{ox} \cdot C_{B,th}}{C_{ox} + C_{B,th}} = C_{ox} \cdot \frac{C_{B,th} / C_{ox}}{1 + C_{B,th} / C_{ox}}$$

$$C_{mos,th} = C_{ox} \cdot \frac{n-1}{n} = 7 [pF]$$

$$C_{ox} C_{D,th}$$

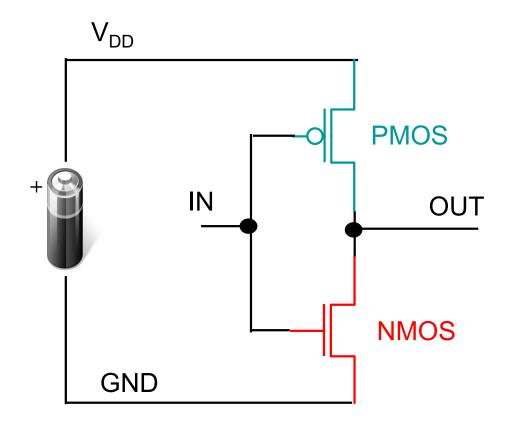

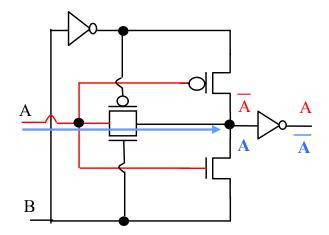

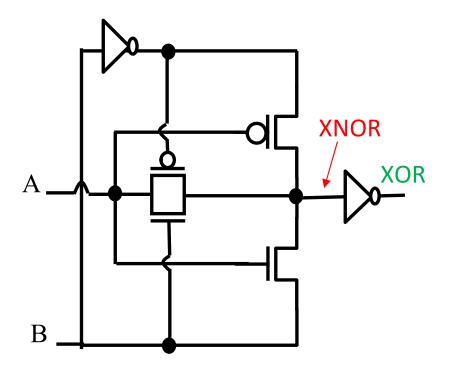

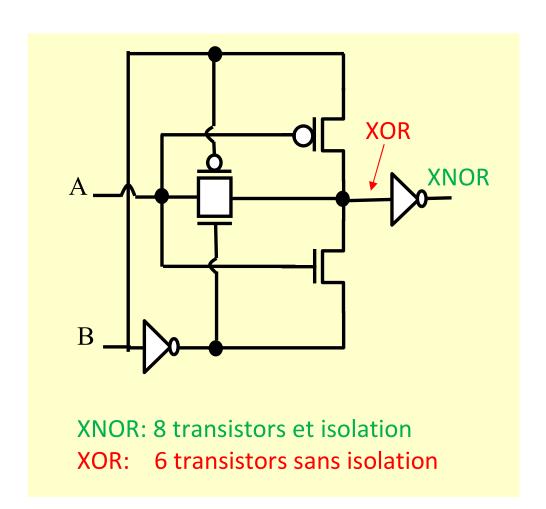

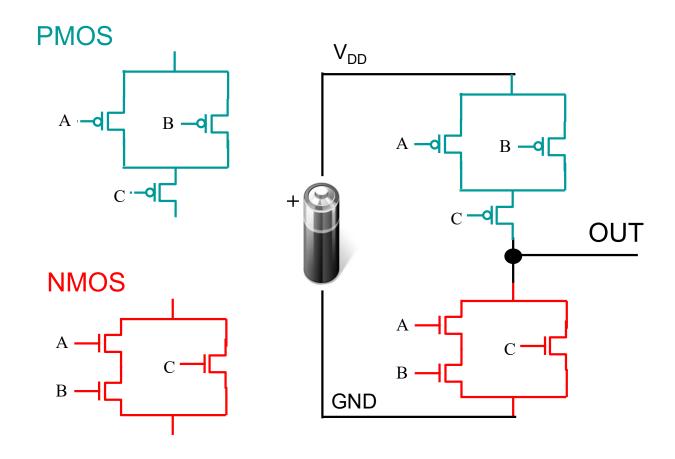

#### XOR avec 8 transistors

(voir script)

L'inverseur final sert à isoler la sortie de l'entrée!

| A | В |   | OUT |

|---|---|---|-----|

| 0 | 0 | 1 | 0   |

| 1 | 0 | 0 | 1   |

| 0 | 1 | 0 | 1   |

| 1 | 1 | 1 | 0   |

**XNOR XOR**

XOR: 8 transistors et isolation

XNOR: 6 transistors sans isolation

(voir script) AOI-21  $\rightarrow$  [(A et B) ou C]

### And-Or-Invert

|     | Α | В | С | AOI-21 |

|-----|---|---|---|--------|

|     | 0 | 0 | 0 | 1      |

| OR  | 0 | 0 | 1 | 0      |

|     | 0 | 1 | 0 | 1      |

|     | 0 | 1 | 1 | 0      |

|     | 1 | 0 | 0 | 1      |

|     | 1 | 0 | 1 | 0      |

| AND | 1 | 1 | 0 | 0      |

|     | 1 | 1 | 1 | 0      |

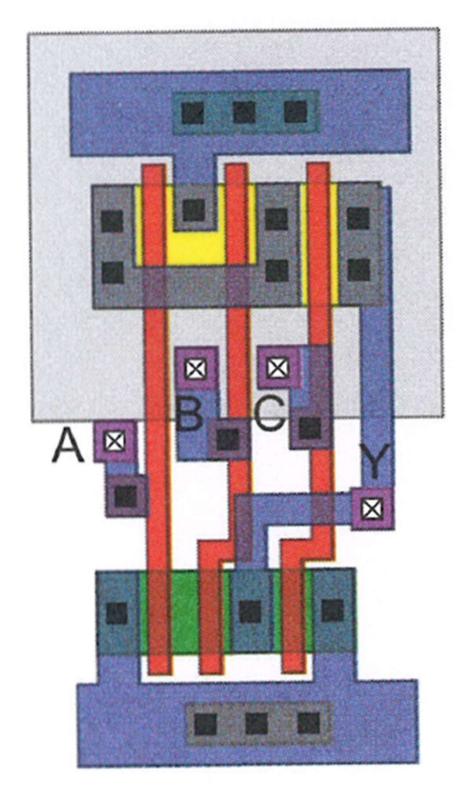

# Layout AOI-21 «And-Or-Invert»

Weste/Harris, « CMOS VLSI design », Addison-Wesley